Mga produkto

-

Deye SUN-20K-SG01HP3-EU-AM2 Taas nga Boltahe nga Hybrid Inverter

Deye SUN-20K-SG01HP3-EU-AM2 Taas nga Boltahe nga Hybrid Inverter

- Gahum:50kW, 40kW, 30kW

- Temperatura Range:-45~60 ℃

- Sakup sa Boltahe:160~800V

- Gidak-on:527*894*294MM

- Timbang:75KG

- Garantiya:5 ka tuig

-

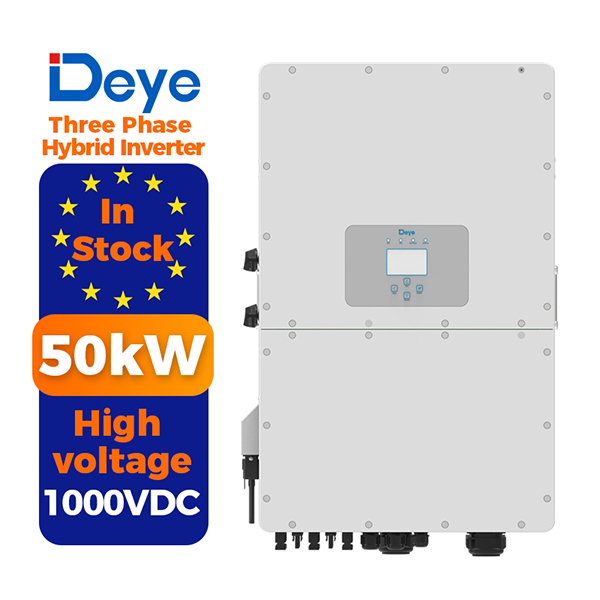

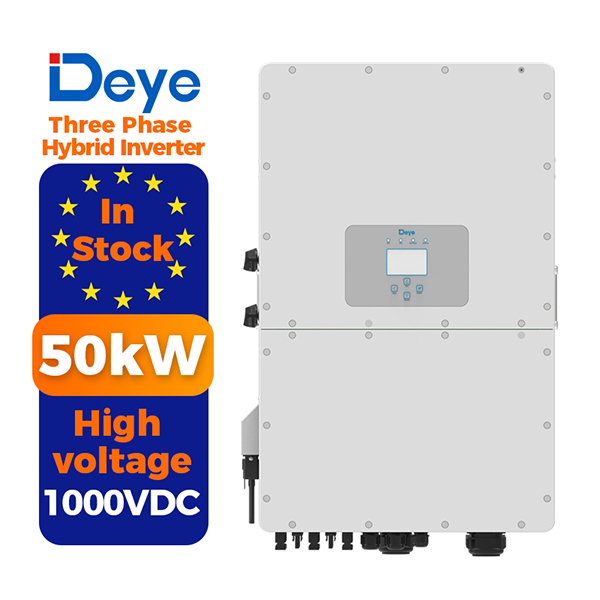

Deye SUN-50K-SG01HP3-EU-BM4 Taas nga Boltahe nga Hybrid Inverter

Deye SUN-50K-SG01HP3-EU-BM4 Taas nga Boltahe nga Hybrid Inverter

- Gahum:50kW, 40kW, 30kW

- Temperatura Range:-45~60 ℃

- Sakup sa Boltahe:160~800V

- Gidak-on:527*894*294MM

- Timbang:75KG

- Garantiya:5 ka tuig

-

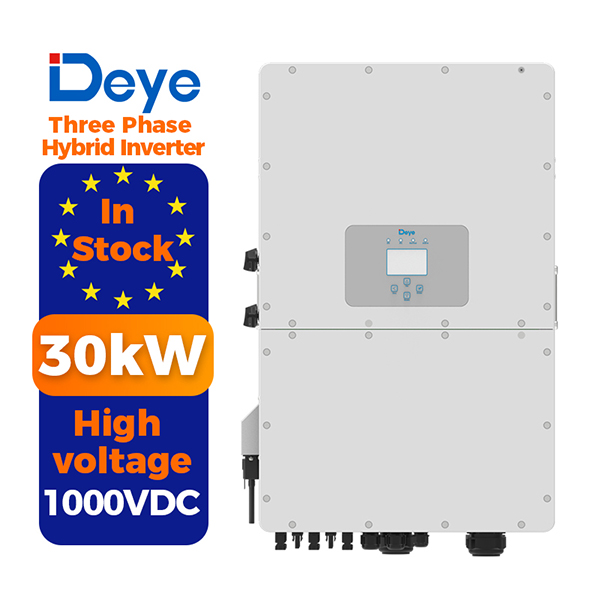

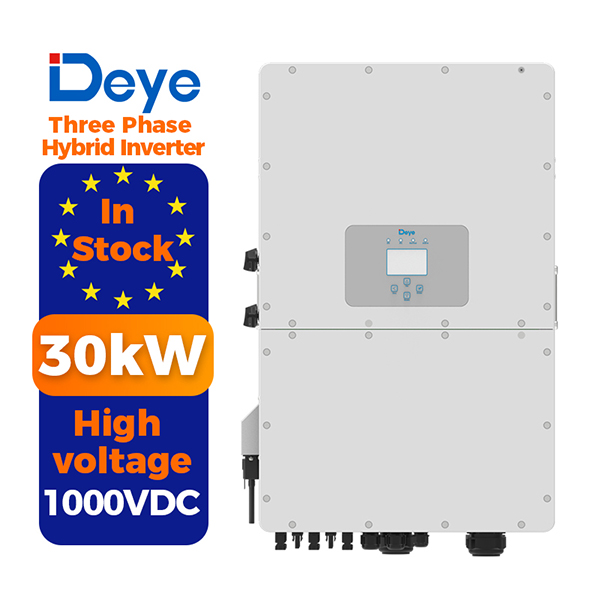

Deye SUN-30K-SG01HP3-EU-BM4 Taas nga Boltahe nga Hybrid Inverter

Deye SUN-30K-SG01HP3-EU-BM4 Taas nga Boltahe nga Hybrid Inverter

- Gahum:50kW, 40kW, 30kW

- Temperatura Range:-45~60 ℃

- Sakup sa Boltahe:160~800V

- Gidak-on:527*894*294MM

- Timbang:75KG

- Garantiya:5 ka tuig

-

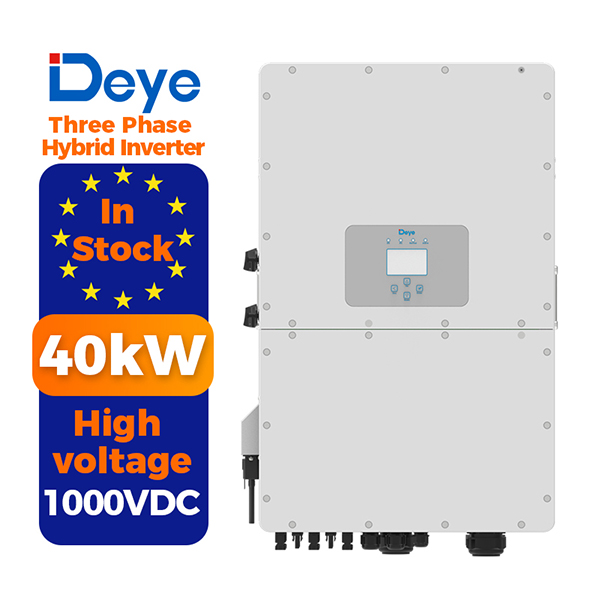

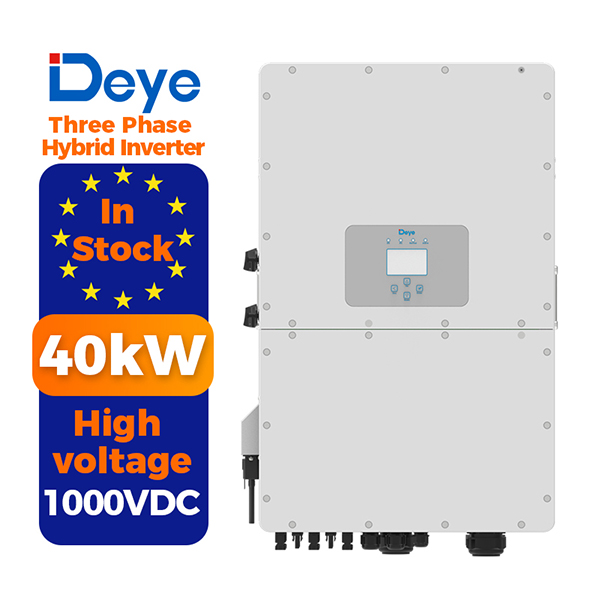

Deye SUN-40K-SG01HP3-EU-BM4 Taas nga Boltahe nga Hybrid Inverter

Deye SUN-40K-SG01HP3-EU-BM4 Taas nga Boltahe nga Hybrid Inverter

- Gahum:50kW, 40kW, 30kW

- Temperatura Range:-45~60 ℃

- Sakup sa Boltahe:160~800V

- Gidak-on:527*894*294MM

- Timbang:75KG

- Garantiya:5 ka tuig

-

MENRED 3.5kW Inverter 5.83kWh Battery All-In-One Home Storage System

MENRED 3.5kW Inverter 5.83kWh Battery All-In-One Home Storage System

Kini nga residential ESS adunay 3.5kW off-grid single-phase inverter ug 5.83kWh battery module.

Ang among off-grid AIO energy storage system adunay bahin nga adunay integrated AC charger, hangtod sa 80A charging current.

Ang among BMS nakigsulti sa mga inverters pinaagi sa CAN protocol, nga nagdugang sa kalig-on sa mga sistema ug tibuok kinabuhi.

-

800.png)

NEOVOLT 3.6/5kW Inverter 10kWh Battery All-In-One Home Storage System

NEOVOLT 3.6/5kW Inverter 10kWh Battery All-In-One Home Storage System

Kini nga residential ESS adunay 3.6/5kW hybrid single-phase inverter ug 10kWh battery module.

Kini nga produkto makakuha og mas tukma nga datos alang sa mas estrikto nga mga kinahanglanon sa VPP.

Usab, sa off-grid nga senaryo, kini nga usa adunay mas maayo nga pasundayag ug mahimong magkaparehas.

-

Talesun Bistar 10BB Half-cut Mono Perc 108 half cell 395 – 415W TP7F54M

Talesun Bistar 10BB Half-cut Mono Perc 108 half cell 395 – 415W TP7F54M

10BB half-cut cell technology: Bag-ong circuit design, Ga dopped wafer, attenuation<2% (1st year) / ≤0.55% (Linear)

Mahinungdanon nga pagpaubos sa risgo sa init nga lugar: Espesyal nga disenyo sa sirkito nga adunay mas ubos nga temperatura sa init nga lugar

Ubos nga LCOE: 2% dugang nga power generation, ubos nga LCOE

Maayo kaayo nga pasundayag sa Anti-PID: 2 ka beses nga standard sa industriya nga pagsulay sa Anti-PID pinaagi sa TUV SUD

IP68 junction box: Taas nga lebel sa tubig.

-

Talesun Bistar 10BB Half-cut Mono Perc 144 half cell 530 – 550W TP7F72M

Talesun Bistar 10BB Half-cut Mono Perc 144 half cell 530 – 550W TP7F72M

10BB half-cut cell technology: Bag-ong circuit design, Ga dopped wafer, attenuation<2% (1st year) / ≤0.55% (Linear)

Mahinungdanon nga pagpaubos sa risgo sa init nga lugar: Espesyal nga disenyo sa sirkito nga adunay mas ubos nga temperatura sa init nga lugar

Ubos nga LCOE: 2% dugang nga power generation, ubos nga LCOE

Maayo kaayo nga pasundayag sa Anti-PID: 2 ka beses nga standard sa industriya nga pagsulay sa Anti-PID pinaagi sa TUV SUD

IP68 junction box: Taas nga lebel sa tubig.

-

Hoymiles 800W 1000W Micro Inverter HMS-600 HMS-800 HMS-1500 HMS-2000 Microinverter

Hoymiles 800W 1000W Micro Inverter HMS-600 HMS-800 HMS-1500 HMS-2000 Microinverter

Uban sa usa ka gahum sa output nga hangtod sa 400 VA, ang bag-ong microinverter sa Hoymiles nga HMS-400 ranggo taliwala sa labing kataas alang sa 1-in-1 nga microinverter.

Kini nga modelo nasangkapan sa reaktibo nga pagkontrol sa kuryente ug makatagbo sa mga regulasyon sa grid.

Ang bag-ong Sub-1G wireless nga solusyon makahimo sa mas lig-on nga komunikasyon ubos sa lain-laing mga kahimtang sa kinaiyahan.

800.png)